# Actuating, Sensing and Control Mechatronic Systems

# System on Chip

Grzegorz Góra PhD

D1-Lab 20

ggora@agh.edu.pl

http://home.agh.edu.pl/~ggora/

Department of Robotics and Mechatronics

Faculty of Mechanical Engineering and Robotics

AGH University of Science and Technology

#### **AGENDA**

- 1. SoC = FPGA + HPS (MCU)

- 2. Power Configurations

- 3. FPGA and HPS Communications

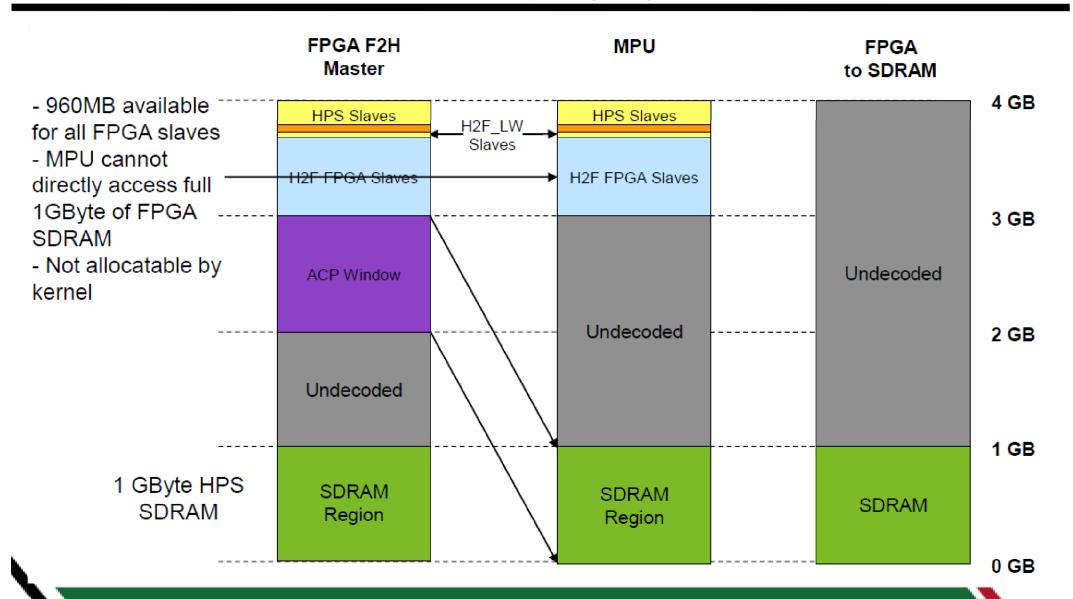

- 4. Memory mapping

- 5. SD Card Image

- 6. HSP Peripherals

- 7. HPS Booting Process

- 8. DE10-Nano

### Cyclone V SoC FPGA + HPS

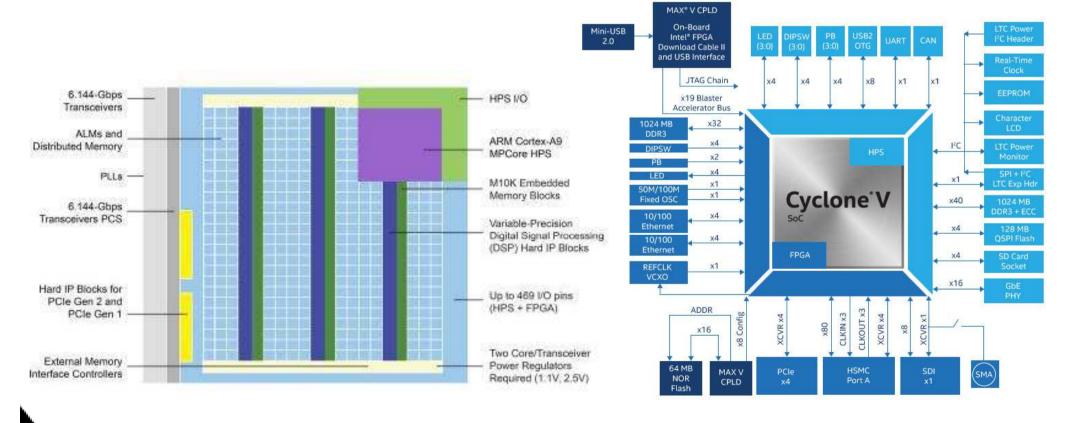

Cyclone V SoC FPGA devices offer a dual-core Arm Cortex-A9 MPCore processor surrounded by rich peripherals and a hardened memory controller. The FPGA fabric is connected to the hard processor system (HPS) through a high-speed >100Gbps interconnect backbone.

# **Cyclone V SoC**Possible HPS and FPGA Power Configurations

The HPS and FPGA portions of the device have separate external power supplies and are power on independently. You can power on the HPS without powering on the FPGA side of the device. However, to power on the FPGA portion, the HPS must already be on or powered on at the same time as the FPGA portion.

| <b>HPS Power</b> | <b>FPGA Power</b> |

|------------------|-------------------|

| On               | On                |

| On               | Off               |

| Off              | Off               |

Therefore, it is possible to use the Cyclone V SoC in 3 different configurations:

- > FPGA-only,

- > HPS-only,

- > HPS & FPGA.

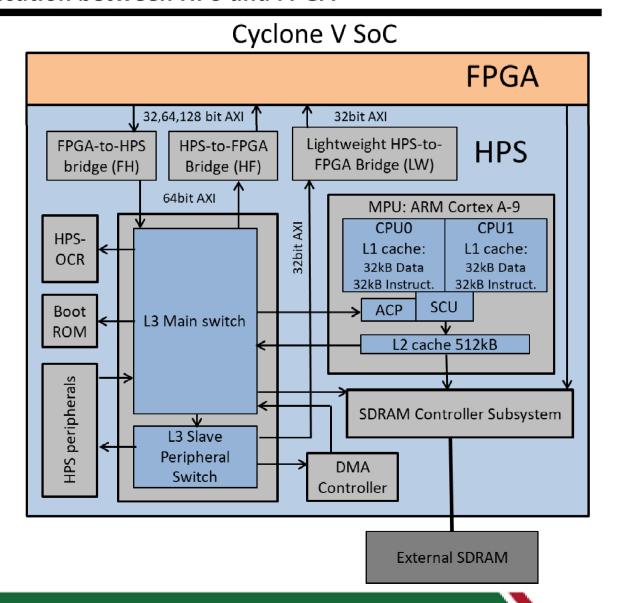

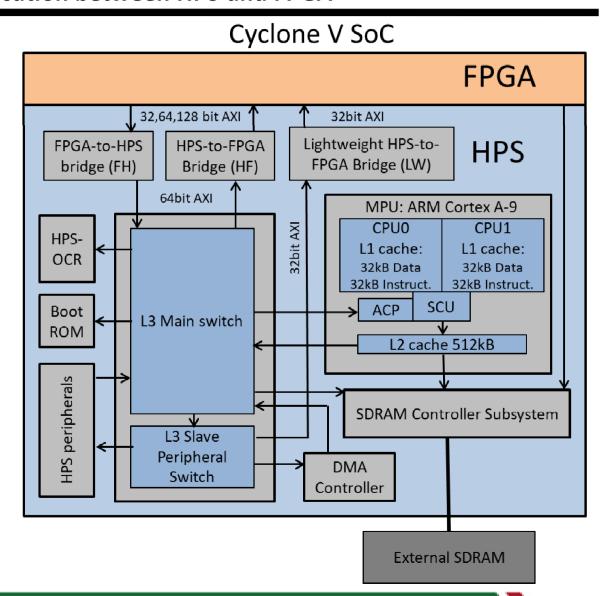

# Cyclone V SoC Communication between HPS and FPGA

Generally communication between HPS and FPGA in Cyclone V SoC devices can be accomplished in the following ways:

### 1) HPS-to-FPGA bridge

A high performance interface from HPS to FPGA. Transactions are usually conducted by the processor or Direct Memory Access (DMA) controllers present in HPS. Bridge is used for accessing FPGA logic, peripherals and memory.

### 2) HPS-to-FPGA Lightweight bridge

A low performance interface to the FPGA fabric. Usually used by the processor to access control and status registers of the components implemented into FPGA.

# Cyclone V SoC Communication between HPS and FPGA

Generally communication between HPS and FPGA in Cyclone V SoC devices can be accomplished in the following ways:

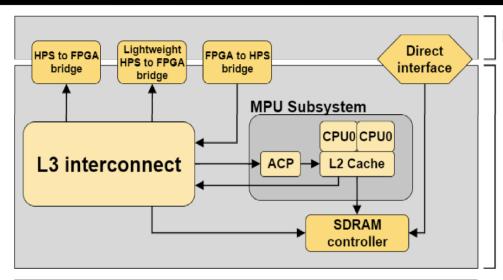

### 3) FPGA-to-HPS bridge

A high performance interface from FPGA to HPS peripherals and memory. Cached memory transactions are supported by adopting ARMs Accelerator Coherency Port (ACP).

### 4) FPGA-to-HPS SDRAM interface

A high performance interface from FPGA to HPS SDRAM controller. FPGA master has access to the processor's RAM. Data residing in processor's cache will result in errors, this issue must be addressed by the software.

## Cyclone V SoC FPGA to SDRAM data transfer

HPS

| Data path         | Bus width | Maximum    | Saturation |  |

|-------------------|-----------|------------|------------|--|

| тата раш          | Dus widin | throughput | frequency  |  |

|                   | 32 bits   | 5.05 Gbps  | 120 MHz    |  |

| FPGA-L3-SDRAM     | 64 bits   | 10.10 Gbps | 120 MHz    |  |

|                   | 128 bits  | 10.52 Gbps | 65 MHz     |  |

| FPGA-L3-ACP-SDRAM | 32 bits   | 6.90 Gbps  | -          |  |

|                   | 64 bits   | 8.64 Gbps  | 120 MHz    |  |

|                   | 128 bits  | 11.26 Gbps | 90 MHz     |  |

|                   | 32 bits   | 7.52 Gbps  | -          |  |

| FPGA-SDRAM        | 64 bits   | 14.64 Gbps | -          |  |

| TT GA-SDRAW       | 128 bits  | 17.68 Gbps | 80 MHz     |  |

|                   | 256 bits  | 20.08 Gbps | 45 MHz     |  |

# FPGA to SDRAM data transfer:

> FPGA-SDRAM - FPGA Master directly interacts with SDRAM controller.

➤ **FPGA-L3-SDRAM** — FPGA Master interacts with SDRAM controller via L3 interconnect.

➤ FPGA-L3-ACP-SDRAM — FPGA Master interacts with SDRAM controller via L3 interconnect and ACP.

www.agh.edu.pl

## Cyclone V SoC Memory Map

## Cyclone V SoC SD Card Image

Partition 3

Type=A2 (raw)

Partition 2

Type=83 (EXT Linux)

Partition 1

Type=B (FAT32 Windows)

U-boot Environment Settings

Master Boot Record

(MBR)

| Location               | File Name      | Desciption                                            |  |

|------------------------|----------------|-------------------------------------------------------|--|

| Partition 1<br>(FAT32) | socfpga.dtb    | Device Tree Blob                                      |  |

|                        | soc_system.rbf | FPGA configuration file                               |  |

|                        | u-boot.scr     | U-Boot script:<br>configures FPGA and<br>loads kernel |  |

|                        | zlmage         | Compressed Linux kernel image file                    |  |

| Partition 2<br>(EXT3)  | Various        | Linux root file system                                |  |

| Partition 3            | n/a            | Preloader image(s)                                    |  |

| (A2 raw)               | n/a            | U-Boot image                                          |  |

## Cyclone V SoC HSP Peripherals

# Possibilities of using HPS peripheral systems:

- HSP Peripherals (e.g.: UART, SPI) + dedicated HPS pins;

- HPS Peripherals + any FPGA pins;

- HPS pins as GPIO;

- FPGA pins controlled by HPS (LOANIO).

# Cyclone V SoC HSP Peripherals Mux Table

| RGMII0_TX_CLK |                        |                     | EMACO.TX_CLK (Set0)    | GPIO00 | LOANIO00 |

|---------------|------------------------|---------------------|------------------------|--------|----------|

| RGMIIO TXDO   |                        | USB1.D0 (Set0)      | EMAC0.TXD0 (Set0)      | GPIO01 | LOANIO01 |

| GMII0_TXD1    |                        | USB1.D1 (Set0)      | EMAC0.TXD1 (Set0)      | GPIO02 | LOANIO02 |

| RGMII0_TXD2   |                        | USB1.D2 (Set0)      | EMAC0.TXD2 (Set0)      | GPIO03 | LOANIO03 |

| RGMIIO_TXD3   |                        | USB1.D3 (Set0)      | EMAC0.TXD3 (Set0)      | GPIO04 | LOANIO04 |

| RGMIIO_RXD0   |                        | USB1.D4 (Set0)      | EMACO RXD0 (Set0)      | GPI005 | LOANIO05 |

| RGMIIO_MDIO   | (2C2.SDA (Set0)        | USB1.D5 (Set0)      | EMAC0.MDIO (Set0)      | GPIO08 | LOANIO08 |

| RGMIIO_MDC    | (2C2.SCL (Set0)        | USB1.D6 (Set0)      | EMAC0.MDC (Set0)       | GP1007 | LOANIO07 |

| RGMIIO_RX_CTL |                        | USB1.D7 (Set0)      | EMACO.RX_CTL (Set0)    | GPIO08 | LOANIO08 |

| GMIIO_TX_CTL  |                        |                     | EMAC0.TX_CTL (Set0)    | GP1009 | LOANIO09 |

| GMII0_RX_CLK  |                        | USB1.CLK (Set0)     | EMACO.RX_CLK (Set0)    | GPIO10 | LOANIO10 |

| GMII0_RXD1    |                        | USB1.STP (Set0)     | EMAC0.RXD1 (Set0)      | GPIO11 | LOANIO11 |

| RGMII0_RXD2   |                        | USB1.DIR (Set0)     | EMAC0.RXD2 (Set0)      | GPIO12 | LOANIO12 |

| GMII0_RXD3    |                        | USB1.NXT (Set0)     | EMAC0.RXD3 (Set0)      | GPIO13 | LOANIO13 |

| IAND_ALE      | QSPI.SS3 (Set1) (Set0) | EMAC1.TX_CLK (Set0) | NAND.ALE (Set0)        | GPIO14 | LOANIO14 |

| AND_CE        | USB1.D0 (Set1)         | EMAC1.TXD0 (Set0)   | NAND.CE (Set0)         | GPI015 | LOANIO15 |

| AND_CLE       | USB1.D1 (Set1)         | EMAC1.TXD1 (Set0)   | NAND.CLE (Set0)        | GPIO16 | LOANIO16 |

| AND_RE        | USB1 D2 (Set1)         | EMAC1.TXD2 (Set0)   | NAND.RE (Set0)         | GP(017 | LOANIO17 |

| AND_RB        | USB1 D3 (Set1)         | EMAC1.TXD3 (Set0)   | NAND.RB (Set0)         | GPI018 | LOANIO18 |

| AND_DQ0       |                        | EMAC1.RXD0 (Set0)   | NAND.DQ0 (Set0)        | GPI019 | LOANIO19 |

| AND_DQ1       | (2C3.SDA (Set0)        | EMAC1.MDIO (Set0)   | NAND.DQ1 (Set0)        | GP1020 | LOANIO20 |

| AND_DQ2       | (2C3 SCL (Set0)        | EMAC1.MDC (Set0)    | NAND.DQ2 (Set0)        | GPIO21 | LOANIO21 |

| AND_DQ3       | USB1.D4 (Set1)         | EMAC1.RX_CTL (Set0) | NAND.DQ3 (Set0)        | GPIO22 | LOANIO22 |

| AND_DQ4       | USB1.D5 (Set1)         | EMAC1.TX_CTL (Set0) | NAND.DQ4 (Set0)        | GPIO23 | LOANIO23 |

| AND_DQ5       | USB1.D6 (Set1)         | EMAC1.RX_CLK (Set0) | NAND.DQ5 (Set0)        | GPIO24 | LOANIO24 |

| IAND_DQ6      | USB1.D7 (Set1)         | EMAC1.RXD1 (Set0)   | NAND.DQ6 (Set0)        | GP1025 | LOANIO25 |

| AND_DQ7       |                        | EMAC1.RXD2 (Set0)   | NAND.DQ7 (Set0)        | GPIO28 | LOANIO26 |

| AND_WP        | QSPI.SS2 (Set1) (Set0) | EMAC1.RXD3 (Set0)   | NAND.WP (Set0)         | GP1027 | LOANIO27 |

| IAND_WE       |                        | QSPI.SS1 (Set0)     | NAND.WE (Set0)         | GPIO28 | LOANIO28 |

| SPI_IO0       | USB1.CLK (Set1)        |                     | QSPI.IO0 (Set1) (Set0) | GP1029 | LOANIO29 |

| SPI_IO1       | USB1.STP (Set1)        |                     | QSPI.IO1 (Set1) (Set0) | GPIO30 | LOANIO30 |

| SPI_IO2       | US61.DIR (Set1)        |                     | QSPI.IO2 (Set1) (Set0) | GPI031 | LOANIO31 |

| SPI_103       | USB1 NXT (Set1)        |                     | QSPI.IO3 (Set1) (Set0) | GPI032 | LOANIO32 |

| SPI_SS0       |                        |                     | QSPLSS0 (Set1) (Set0)  | GPI033 | LOANIO33 |

| QSPI_CLK      |                        |                     | QSPI.CLK (Set1) (Set0) | GPI034 | LOANIO34 |

| QSPI_SS1      |                        |                     | QSPLSS1 (Set1)         | GPIO35 | LOANIO35 |

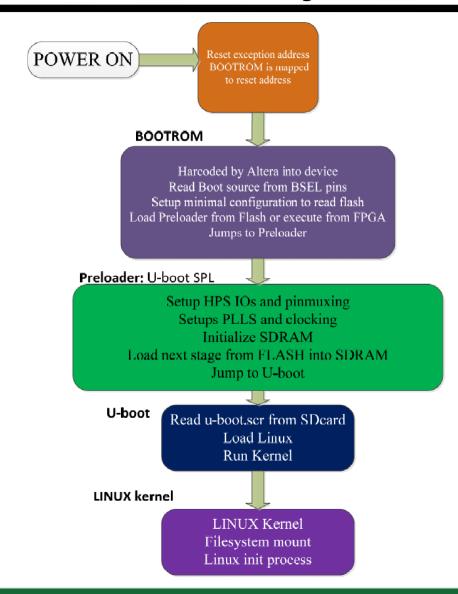

## Cyclone V SoC HPS Booting Process

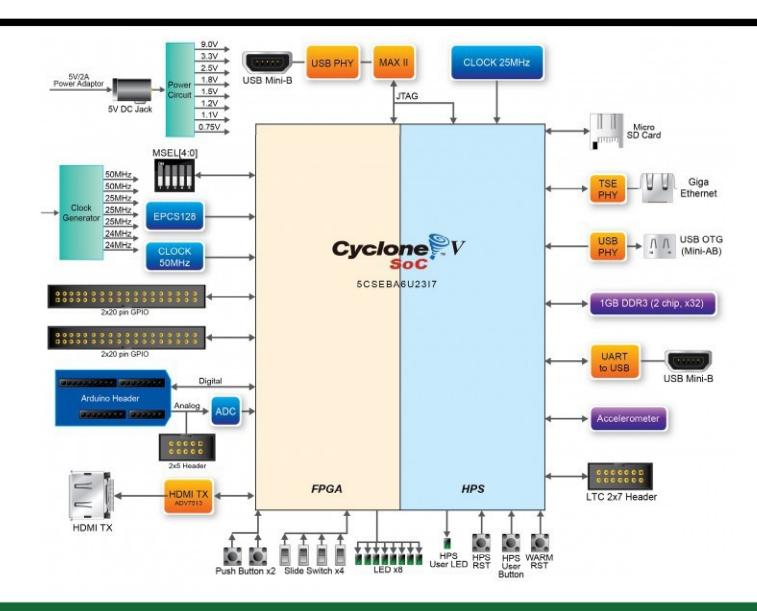

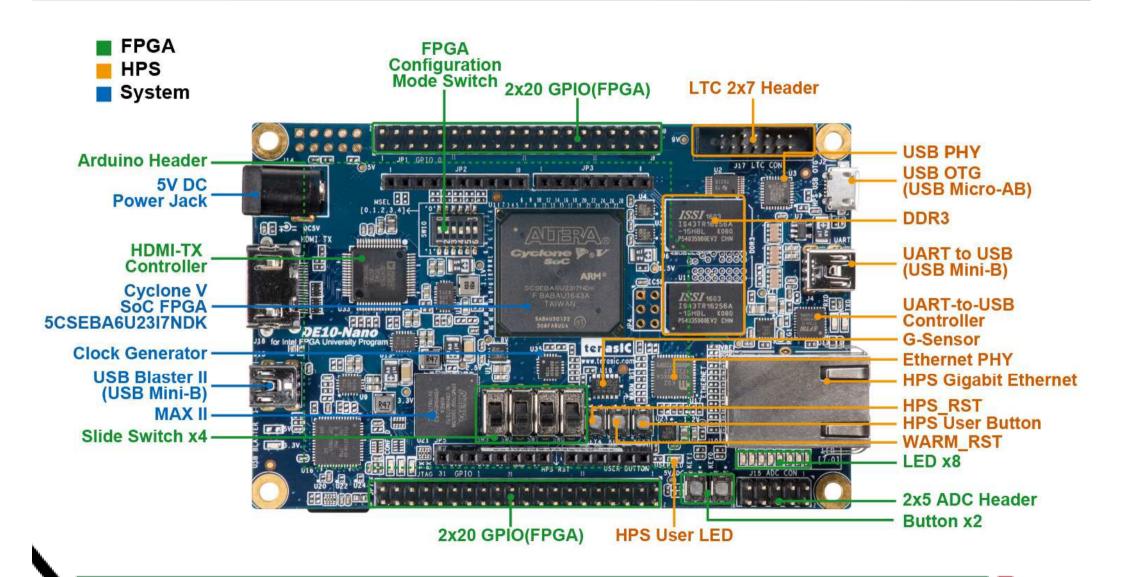

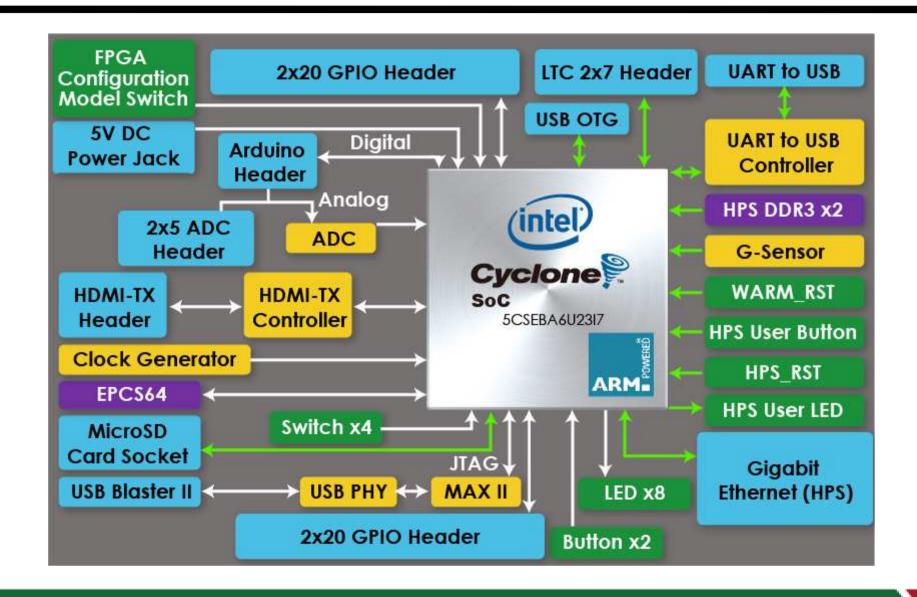

#### DE10 -Nano

#### DE10 -Nano

#### DE10 - Nano

#### DE10 - Nano

#### **FPGA Device**

- ➤ Intel Cyclone® V SE 5CSEBA6U23I7 device (110K LEs)

- ➤ Serial configuration device EPCS64 (revision B2 or later)

- ➤ USB-Blaster II onboard for programming; JTAG Mode

- > HDMI TX, compatible with DVI 1.0 and HDCP v1.4

- ➤ 2 push-buttons

- > 4 slide switches

- > 8 green user LEDs

- ➤ Three 50MHz clock sources from the clock generator

- > Two 40-pin expansion headers

- ➤ One Arduino expansion header (Uno R3 compatibility), can be connected with Arduino shields

- ➤ One 10-pin Analog input expansion header (shared with Arduino Analog input)

- ➤ A/D converter, 4-pin SPI interface with FPGA

#### **HPS (Hard Processor System)**

- ➤ 800MHz Dual-core ARM Cortex-A9 processor

- > 1GB DDR3 SDRAM (32-bit data bus)

- ➤ 1 Gigabit Ethernet PHY with RJ45 connector

- > USB OTG Port, USB Micro-AB connector

- ➤ Micro SD card socket

- ➤ Accelerometer (I2C interface + interrupt)

- ➤ UART to USB, USB Mini-B connector

- > Warm reset button and cold reset button

- > One user button and one user LED

- > LTC 2x7 expansion header

### **BIBLIOGRAPHY**

[1] dr hab. inż. Maciej Petko, prof. AGH - Wykład