Projekty

rcore

rcore jest 32-bitowym mikroprocesorem RISC-V, wspierającym zbiór instrukcji RV32I. Układ jest rozwijany jako dwustopniowy mikroprocesor o architekturze harwardzkiej, zaprojektowany w języku SystemVerilog.pxrv

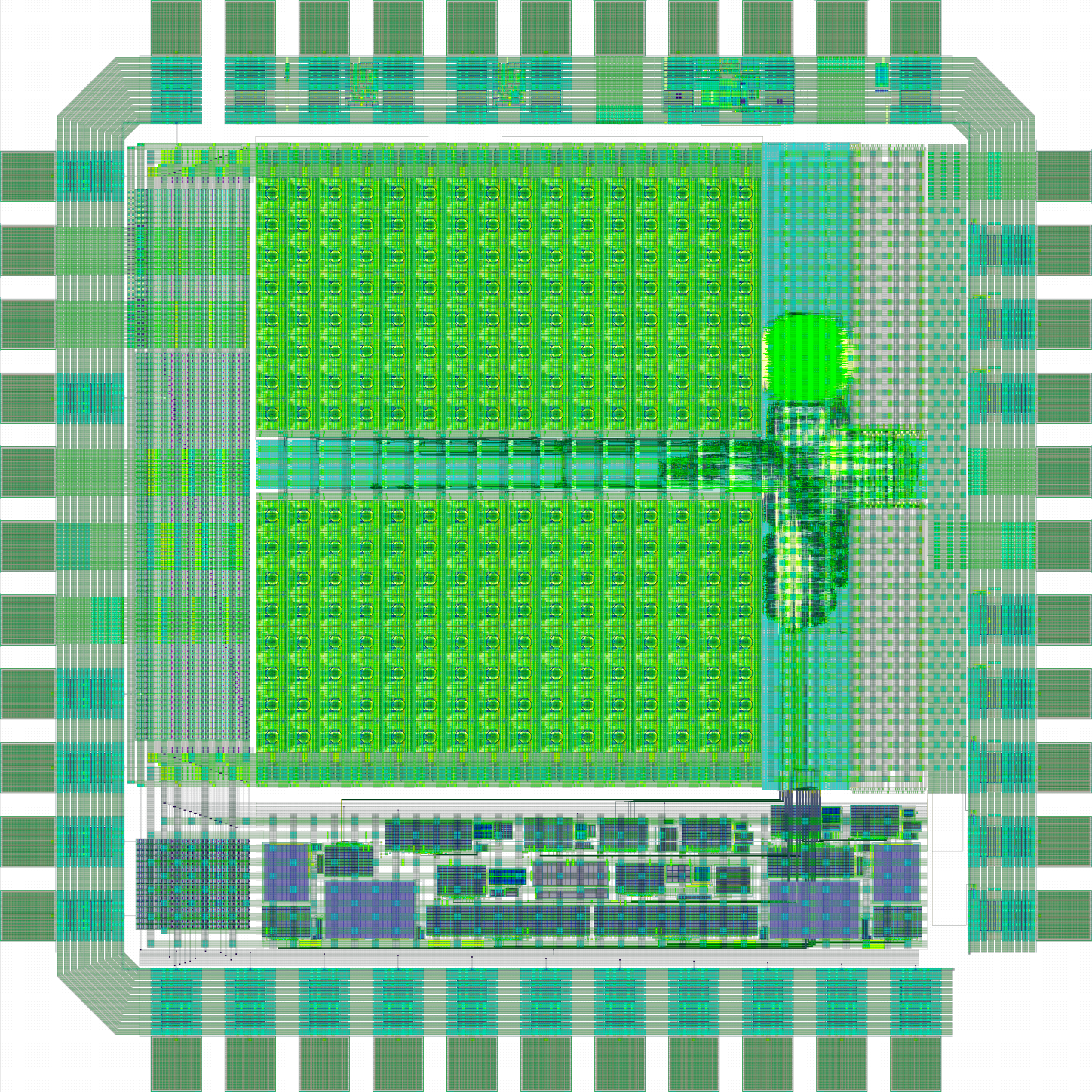

PXRV jest, według najlepszej wiedzy Autora, pierwszym na świecie układem scalonym integrującym we wspólnym podłożu krzemowym mikroprocesor RISC-V oraz układ odczytowy dla hybrydowego pikselowego detektora promieniowania jonizującego.Literatura:

- Readout chip with RISC-V microprocessor for hybrid pixel detectors ,

- Development of On-Chip Calibration for Hybrid Pixel Detectors .

pxrv_controller

pxrv_controller jest systemem testowym skonstruowanym do testowania układu scalonego pxrv. System ten składał się z dwóch aplikacji testowych działających w przestrzeni użytkownika, sterownika działającego w przestrzeni jądra oraz sprzętowego interfejsu zaimplementowanego w układzie FPGA Intel Arria 10 GX. Komunikacja pomiędzy komputerem a układem FPGA zrealizowana została za pośrednictwem interfejsu PCIe Gen. 3.pidpix_controller

pidpix_controller jest systemem testowym skonstruowanym do testowania układu scalonego PIDPIX. Podobnie jak w przypadku projektu pxrv_controller, w projekcie zastosowana została architektura Linux-PCIe-FPGA.Literatura: